Digital hardware enthusiasts are well aware that at this stage, chips (including processors, especially desktop processors) have reached a bottleneck. The difficulty of research and development is increasing, costs are rising, and performance improvements are slowing down, resulting in overall dissatisfaction. This situation is actually due to a variety of factors.

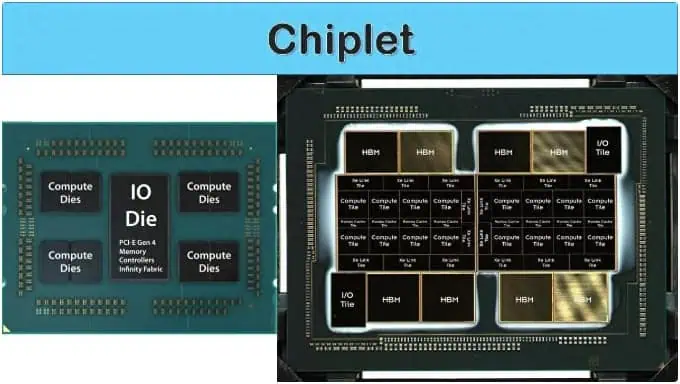

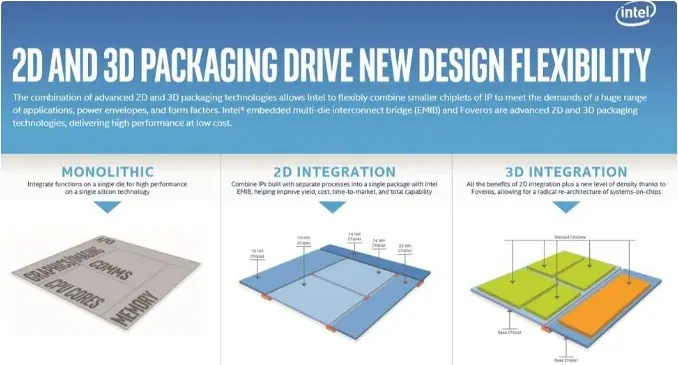

To address this issue, one feasible solution is to divide a large chip into several smaller chips (Chiplets) and then package them together. This approach can reduce development difficulty and manufacturing costs, making performance improvements easier to achieve.

However, when packaging multiple small chips together, interconnect standards must be considered, requiring a comprehensive approach from chip design to final manufacturing. This is a complex and extensive task that no single company can accomplish alone. It requires collaborative efforts across the entire upstream and downstream industry chain.

The UCIe (Universal Chiplet Interconnect Express) Alliance is an organization of this nature. Established in March 2022, it is an open industry alliance.

The organization’s goal is to jointly establish interconnect standards between small chips, making it easier for chip manufacturers to develop, build, and manage system-level packages that include chips from different vendors.

The alliance’s major members include industry giants such as Intel, AMD, Arm, Qualcomm, TSMC, Samsung, ASE, Google Cloud, Meta, and Microsoft, giving it significant influence in the industry.

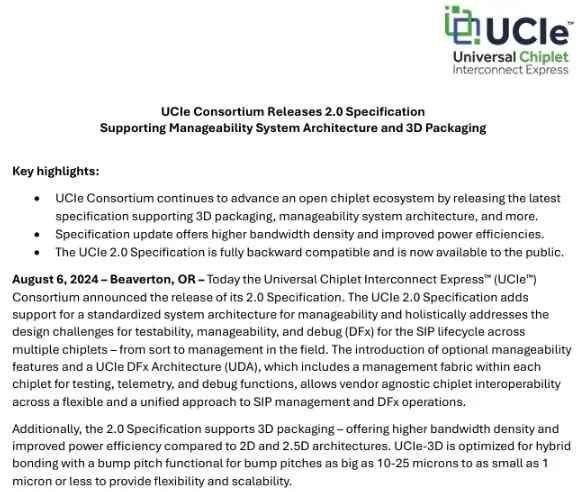

On August 6th, the UCIe Alliance released the latest UCIe 2.0 version, further simplifying and standardizing relevant standards, while also adding certain features.

Currently, if small chips come from multiple vendors, multiple management frameworks must be used for each chip during packaging. The UCIe 2.0 specification simplifies this process by introducing a standardized manageability system architecture, which addresses manageability, testability, and easier debugging across multiple chips throughout the packaging process.

The UCIe 2.0 specification also defines an optional UCIe DFx architecture (UDA), which allows vendor-independent testing, telemetry, and debugging functions to be integrated into each chiplet, simplifying the development and debugging of multi-chip system-level packaging.

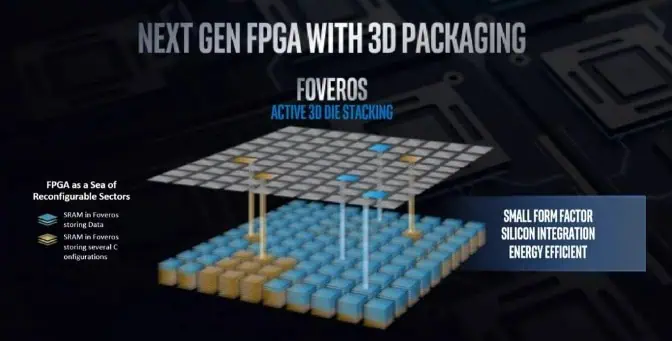

One of the important improvements and features of the UCIe 2.0 specification is support for 3D packaging, which, compared to existing 2D and 2.5D packaging technologies, can further improve power efficiency. It is optimized for hybrid bonding, supporting bump sizes of 10 micrometers to 25 micrometers, 1 micrometer, or even smaller, providing greater flexibility and scalability.

Finally, the UCIe 2.0 specification also optimizes the packaging process to ensure interoperability and effective compliance testing. The purpose is to validate the functionality of the device under test based on known good UCIe implementations, essentially establishing an initial framework for testing physical components, adapters, and protocols.

Cheolmin Park, President of the UCIe Alliance and Vice President of Samsung, stated:

“The UCIe Alliance is currently empowering the development and manufacturing of various chiplets to meet the rapidly changing needs of the semiconductor industry. The UCIe 2.0 specification builds on previous iterations (compatible with UCIe 1.0 and UCIe 1.1) by developing comprehensive solutions to reduce the difficulty of interconnection between chiplets. This is the latest progress of the UCIe Alliance in promoting the currently flourishing open chiplet ecosystem.”

Some readers may think that multi-chip 3D packaging technology and the UCIe 2.0 specification are still far from us, but this is not the case. The relevant technologies have already been applied in servers, processors, and some consumer-grade processors, and their future applications and roles will only become increasingly important.

Note: Figures four and five are reference images related to Intel’s technology and are not images presented by the UCIe Alliance; they are provided for reference only.

Disclaimer:

- This channel does not make any representations or warranties regarding the availability, accuracy, timeliness, effectiveness, or completeness of any information posted. It hereby disclaims any liability or consequences arising from the use of the information.

- This channel is non-commercial and non-profit. The re-posted content does not signify endorsement of its views or responsibility for its authenticity. It does not intend to constitute any other guidance. This channel is not liable for any inaccuracies or errors in the re-posted or published information, directly or indirectly.

- Some data, materials, text, images, etc., used in this channel are sourced from the internet, and all reposts are duly credited to their sources. If you discover any work that infringes on your intellectual property rights or personal legal interests, please contact us, and we will promptly modify or remove it.