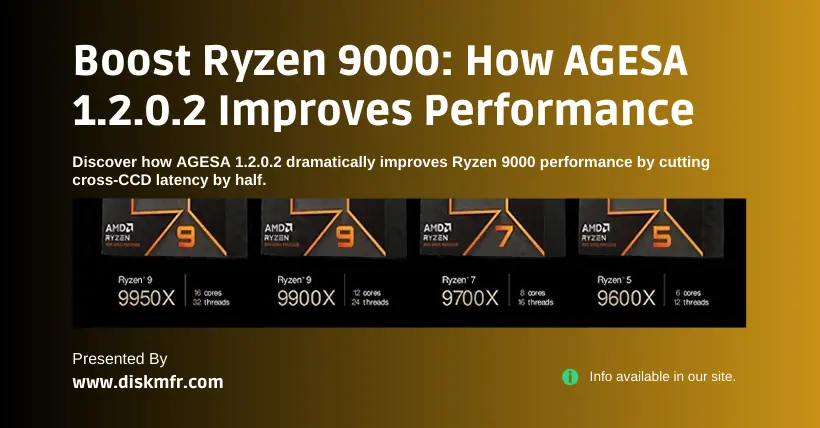

Although the AMD Ryzen 9000 series processors have now been officially released, they have yet to gain full consumer recognition. This is mainly because their actual performance falls significantly short of AMD’s official claims, which is quite embarrassing.

In response, AMD has provided various explanations, generally stating that the Ryzen 9000 series processors have not yet fully unleashed their potential due to several reasons. They have promised to introduce multiple measures to improve performance, and some of these have already been implemented.

For example, they have collaborated with Microsoft to roll out the KB5041587 patch through a Windows update (see Figure 2) and released the AGESA 1.2.0.1 firmware update (see Figure 3), with the latter being the focus of this discussion.

AMD has officially released the AGESA 1.2.0.1 firmware update (essentially the base code for motherboard BIOS), which has been provided to motherboard partners. These partners have also released new BIOS updates that include AGESA 1.2.0.1. Note that the latest version is AGESA 1.2.0.2.

So, what improvements does the AGESA 1.2.0.2 firmware update bring? Why can it boost the performance of the Ryzen 9000 series processors?

At this point, some might say that the AGESA 1.2.0.1 firmware added a 105W power mode (see the figure below), lifting some power limitations, which could improve the multi-core performance of Ryzen 9000 series processors and thereby enhance overall performance.

This answer is correct but incomplete. It’s only part of the story. AMD made another significant improvement in the AGESA 1.2.0.2 firmware update, which is the substantial reduction of cross-CCD latency.

To understand this improvement, you first need to know what “CCD” and “cross-CCD latency” are. For most general tech enthusiasts, these concepts can be a bit complex and challenging to grasp, so I’ll briefly explain them.

The concept of “CCD” applies only to AMD processors. Generally, when discussing “CCD,” another concept, “CCX,” is often mentioned alongside it. They always appear together, and understanding their relationship is crucial.

“CCX” is the basic building block of AMD’s Zen architecture processors. Each CCX typically contains multiple processor cores (the number varies by model), with each core having its own L1 and L2 cache. The cores within a CCX can be individually turned off or disabled, and a CCD is essentially a composite of CCXs.

AMD’s entry-level and mid-range processors usually have one CCD, while high-end models have two CCDs (see the figure above). For example, in Zen 3 architecture processors, each CCD contains one CCX, and each CCX has up to eight cores. The Ryzen 5 5600X has one CCD, with two cores disabled, leaving six cores that share a 32MB L3 cache.

Note that this is just theoretical; in reality, some batches of the Ryzen 5 5600X may have two CCDs, but one is disabled (see the figure below). Some might wonder: if there are two CCDs, why disable one? The simple answer is that the disabled CCD likely has a significant defect that prevents it from functioning properly.

In theory, the more CCDs a processor has, the higher its performance potential. However, more CCDs also bring some issues. Some might think I’m going to talk about power consumption next; indeed, more CCDs generally mean higher power consumption, but that’s only one aspect. The more critical issue is cross-CCD communication latency. If not handled properly, this latency can be high and affect performance.

When multiple CCDs work together, they share a lot of data and need to communicate frequently and closely. Naturally, the shorter the time spent on this, the better the performance. This concept is known as “cross-CCD latency.”

In a processor with a single CCD design, or within a single CCD, the latency between cores may be around 20 to 30 nanoseconds, while cross-CCD latency could reach 70 to 80 nanoseconds, which is the current mainstream level.

In the Ryzen 9000 series, the high-end models Ryzen 9 9900X and Ryzen 9 9950X also use a dual-CCD design. However, at launch, these processors had relatively high cross-CCD latency, generally around 180 nanoseconds (see the figure above), which is one of the reasons their performance was underwhelming.

In the AGESA 1.2.0.2 firmware, AMD has now fixed this issue, cutting cross-CCD latency by half. According to third-party reviews, after updating to the new firmware, cross-CCD latency is reduced to around 75 nanoseconds (see the figure above), which is almost on par with the Ryzen 9 7950X and Ryzen 9 7900X.

Note: In the two images above, the upper left and lower right corners represent the intra-CCD latency statistics, while the lower left and upper right corners represent the cross-CCD latency statistics.

Theoretically, significantly reducing cross-CCD latency should improve processor performance, but the actual impact depends on specific application scenarios. Significant performance gains may only be observed in certain high-load intensive applications and might not be applicable to gaming, as AMD prohibits games from using both CCDs simultaneously.

In conclusion, AMD’s claim that the Ryzen 9000 series processors have not yet fully unleashed their potential is credible. The improvement measures they have introduced are indeed effective and not just empty promises, though further refinement will take some time.

Related:

Disclaimer:

- This channel does not make any representations or warranties regarding the availability, accuracy, timeliness, effectiveness, or completeness of any information posted. It hereby disclaims any liability or consequences arising from the use of the information.

- This channel is non-commercial and non-profit. The re-posted content does not signify endorsement of its views or responsibility for its authenticity. It does not intend to constitute any other guidance. This channel is not liable for any inaccuracies or errors in the re-posted or published information, directly or indirectly.

- Some data, materials, text, images, etc., used in this channel are sourced from the internet, and all reposts are duly credited to their sources. If you discover any work that infringes on your intellectual property rights or personal legal interests, please contact us, and we will promptly modify or remove it.