PCIe development has progressed from the original 1.0 to 6.0. However, many people know about PCIe without understanding its essence. Today, the author will take you to explore. To understand what PCIe is, we first need to discuss what a bus is. If we consider the motherboard as a city, then the bus is like the city’s public bus, which follows a fixed route to continuously transport bits back and forth.

PCIe belongs to high-speed serial point-to-point dual-channel high-bandwidth transmission. The connected devices are allocated dedicated channel bandwidth, not sharing bus bandwidth. It mainly supports active power management, error reporting, end-to-end reliable transmission, hot-plugging, and quality of service (QOS) functions. PCIe’s main advantage is its high data transfer rate, and it has significant development potential.

PCIe also comes in various specifications, such as x1, x4, x8, x16, and x32, where the number following ‘x’ represents how many channels the PCIe slot has (how data enters and exits the PCIe card). A PCIe x1 slot has one channel and can transmit one bit of data per cycle. A PCIe x2 slot has two channels, allowing it to transmit two bits of data per cycle (and so on).

▮ PCIe Interface Speed Rate

▮ PCIe Concepts

Transfer speed is GT/s, not Gbps, as the transfer contains overhead bits that do not provide any additional performance. For example, PCIe 1. x and PCIe 2. x use an 8B/10B encoding scheme, resulting in 20% (= 2/10) of the original channel bandwidth.

GT/s (gigabit transfers per second): Indicates the number of transfer times per second. The approach is to describe the speed characteristics of the physical layer communication protocol, which can be independent of the width of the link.

Gbps (gigabit bits per second): There is no proportional conversion relationship between GT/S and Gbps.

▮ PCIe Bandwidth Calculation

PCIe throughput (available bandwidth) is calculated as follows:

Throughput = Transmission rate * Encoding scheme

For example, the PCI-E2.0 protocol supports 5.0 GT/s, that is, 5G bits can be transmitted per second on each Lane. This does not mean that every Lane of the PCIe 2.0 protocol supports a 5Gbps rate.

Why do we say that? This is because PCIe 2.0 uses the 8B/10B encoding scheme in the physical layer protocol. This means that 10 bits must be sent for every 8 bits transmitted. The two extra bits are not meaningful information for the upper layer.

Then, each Lane of the PCIe 2.0 protocol supports a rate of 5 * 8/10 = 4 Gbps = 500 MB/s.

Take a PCIe 2.0×8 channel as an example. The available bandwidth of x8 is 4 x8 = 32 Gbps = 4 GB/s.

In a similar way

The PCI-E3.0 protocol supports 8.0 GT/s, which means that each Lane can transmit 8 Gbit /s bits per second.

The physical layer protocol of PCIe 3.0 uses a 128B / 130B encoding scheme. That is, 130 bits need to be sent for every 128 bits transmitted.

Then, each Lane of PCIe 3.0 supports a rate of 8 * 128/130 = 7.877 Gbps = 984.6 MB/s.

A PCIe 3.0 x16 channel, x16 available bandwidth is 7.877 x16 = 126.031 Gbps = 15.754 GB/s.

From this, the data in the above table can be calculated.

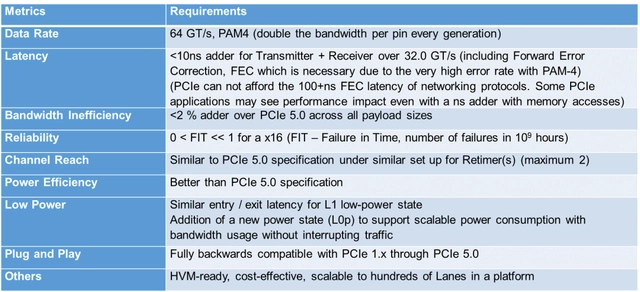

▮ January 2022: PCIe 6.0 was released with a speed of 64 GT/s (Giga Transfers Per Second)

On January 11, 2022, PCI-SIG officially released the final version 1.0 of PCIe 6.0. From a technical perspective, PCIe 6.0 represents the most significant change in nearly 20 years since the introduction of PCIe.

PCIe 6.0 Specification Goals: According to PCI-SIG, PCIe 6.0 introduces three major changes: doubling the data transfer rate from 32 GT/s to 64 GT/s, shifting from NRZ signal mode to PAM4 signal mode for encoding, and transitioning from variable-sized TLP to fixed-size FLIT.

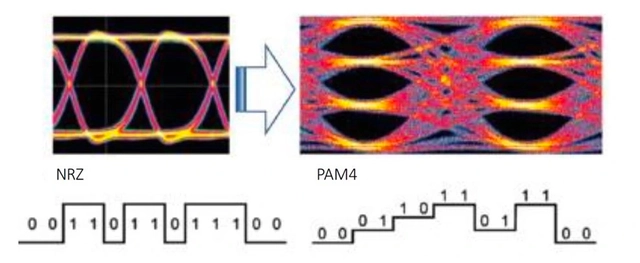

PAM4 Signal

PCIe 6.0 introduces PAM4 encoding, which allows for a doubling of the data transfer rate. Before PCIe 6.0, all previous generations of PCIe used NRZ signaling, which is non-return-to-zero encoding with two voltage levels (0 or 1) and could transmit only 1 bit per clock cycle. PAM4 uses four signal levels, allowing a single signal to represent four different encoding states (00/01/10/11), effectively carrying twice the data of NRZ signaling. However, it comes at the cost of a higher bit error rate (BER).

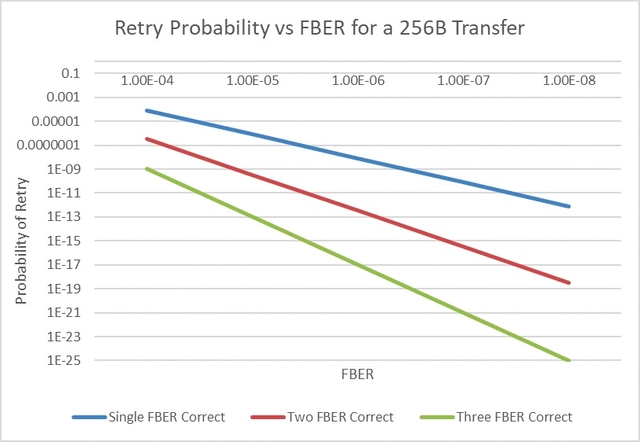

While the PCIe architecture includes Link-Level Retries (LLR) to retransmit transactions affected by errors, the bandwidth losses due to retries make it impractical for PAM4 error rates. Therefore, the PCIe 6.0 specification combines the use of lightweight Forward Error Correction (FEC) and LLR mechanisms to meet low latency and low bandwidth overhead performance metrics. Additionally, the Cyclic Redundancy Check (CRC) scheme provides a robust error detection mechanism to mitigate the high error rates associated with PAM4.

FLIT Mode

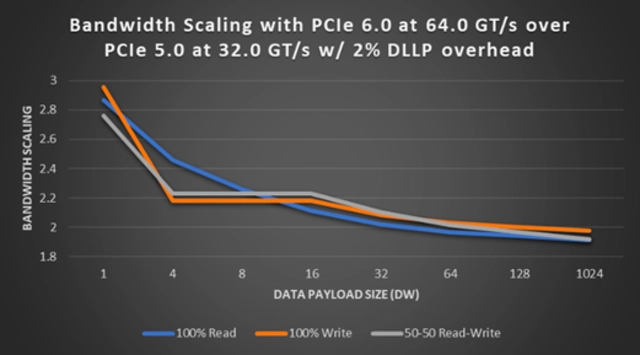

PCIe 6.0 introduces FLIT mode, where data packets are organized into fixed-size flow control units, as opposed to variable sizes in previous generations of PCIe. The initial reason for introducing FLIT mode was to accommodate the use of fixed-size data packets for error correction. However, FLIT mode also simplifies controller-level data management, improving bandwidth efficiency, reducing latency, and minimizing controller footprint. With fixed-size data packets, there’s no longer a need to frame the data packets at the physical layer, saving 4 bytes for each data packet. FLIT encoding also eliminates the previous 128B/130B encoding and Data Link Layer Packet (DLLP) overhead in PCIe specifications, significantly improving TLP efficiency, especially for smaller data packets.

▮ Bonus

| Year | Bandwidth | Frequency/Speed |

|---|---|---|

| 1992 | 133MB/s (32-bit simplex) | 33 Mhz (PCI) |

| 1993 | 533MB/s (64-bit simplex) | 66 Mhz (PCI 2.0) |

| 1999 | 1.06GB/s (64-bit simplex) | 133 Mhz (PCI-X) |

| 2002 | 2.13GB/s (64-bit simplex) | 266 Mhz (PCI-X 2.0) |

| 2002 | 8GB/s (x16 duplex) | 2.5 GHz (PCIe 1. x) |

| 2006 | 16GB/s (x16 duplex) | 5.0 GHz (PCIe 2. x) |

| 2010 | 32GB/s (x16 duplex) | 8.0 GHz (PCIe 3. x) |

| 2017 | 64GB/s (x16 duplex) | 16.0 GHz (PCIe 4.0) |

| 2019 | 128GB/s (x16 duplex) | 32.0 GHz (PCIe 5.0) |

| 2022 | 256GB/s (x16 duplex) | 64.0 GHz (PCIe 6.0) |

Related:

Disclaimer:

- This channel does not make any representations or warranties regarding the availability, accuracy, timeliness, effectiveness, or completeness of any information posted. It hereby disclaims any liability or consequences arising from the use of the information.

- This channel is non-commercial and non-profit. The re-posted content does not signify endorsement of its views or responsibility for its authenticity. It does not intend to constitute any other guidance. This channel is not liable for any inaccuracies or errors in the re-posted or published information, directly or indirectly.

- Some data, materials, text, images, etc., used in this channel are sourced from the internet, and all reposts are duly credited to their sources. If you discover any work that infringes on your intellectual property rights or personal legal interests, please contact us, and we will promptly modify or remove it.