The adoption of new technologies may face some delays.

Earlier this week, PCI-SIG, the organization responsible for developing PCI Express specifications, held the 2024 Developer Conference, where they provided the latest updates on PCIe 6.0 and PCIe 7.0. While progress is being made, it is slower than initially expected. Therefore, the adoption of new technologies may face some delays, as reported by ComputerBase.

In particular, PCI-SIG is delaying the launch of its compliance program. The initial compliance testing for PCIe 6.0 was supposed to start in March but has now been postponed to “Q2,” theoretically meaning it is about to begin. A three-month delay doesn’t seem like a big issue, as the first PCIe 6.0 platforms are set to launch later this year. However, the list of integrators with compliant products won’t be available until 2025. PCIe 6.0 platforms will have to rely on PCIe 5.0 hardware or use PCIe 6.0 components without formal compliance assured by PCI-SIG.

The situation worsens as the PCIe 7.0 compliance program timeline has also changed, pushing compliance testing to 2028 instead of the previously announced 2027. PCIe 7.0 development has reached a 0.5 draft, with the final version 1.0 expected to be released in 2025. This version aims to offer a data transfer rate of 16 GB/s per channel, with a maximum configuration providing 256 GB/s. Duplex operation can achieve rates up to 512 GB/s, double that of PCIe 6.0’s 256 GB/s. However, due to the inability to ensure compatibility between hosts and devices until 2028, PCIe 7.0 won’t really take off until the later part of this decade.

In August 2023, PCI-SIG formed a working group to seek industry input on developing PCIe optical interconnects. The optical working group’s design is technology-agnostic, adaptable to various optical technologies, and may create specific form factors for PCIe solutions. These form factors could include pluggable optical transceivers, on-board optics, co-packaged optics, and optical I/O.

At the developer conference, PCI-SIG provided the latest updates on its optical plans. The group is currently working on updating the logical and electrical layers of the PCIe 6.0 specification to integrate new optical standards. A significant update called Engineering Change Request (ECN) is expected to be completed by December 2024, enhancing existing electrical standards without replacing them. Additionally, the working group has begun work on optical PCIe standardization for the PCIe 7.0 specification, aiming for a 2025 release.

Richard Solomon, Vice President of PCI-SIG, stated: “We received many questions about this issue, like why can’t we go faster? Why does it take so long? What are you doing? The answer is that it takes time from completing the specification to having silicon. Before we have chips, we can’t really create a compliance program. So we start as early as possible, and actually, we are mid-2024. The PCIe 6.0 specification was released in January 2022. It took the industry two years, almost two and a half years, to reach the point where we can test, we have silicon. All these pieces exist. We are actually progressing quite quickly in the compliance program. If this sounds like an excuse, I apologize. It really isn’t. It just explains the things in our schedule.”

Last year, The Next Platform suggested that PCI-SIG needs to speed up its timeline and align the PCI-Express roadmap with the roadmaps of chip manufacturers and server suppliers. It is a widely used interconnect suitable for industries also using Ethernet, InfiniBand, and Nvidia’s proprietary GPU NVLink. As the use of CXL-based tiered and shared main memory increases, the demand for PCI-Express is expected to grow.

However, an organization with so many members—about 970 and growing—and highly scrutinized specifications may not be built for speed. Numerous committees and working groups address possible changes to specifications, FYI pre-tests, FYI tests, and compliance workshops.

“Devices completing our compliance program can choose to be listed on our website, on the innovators list, where members—actually non-SIG members, as it is a publicly accessible website—can view and decide when making purchasing and design decisions, considering which products to consider based on our compliance testing,” Solomon said. “Our compliance program is not a verification or certification program. We are really focused… on interoperability. Our compliance program tests what is most important for interoperability. For such a high-speed signal bus, many tests are electrical tests.”

He noted that with the PCI-Express 7.0 specification expected to be approved sometime between mid to late next year, its integrators list might be released in 2028, adding: “I wish we could do it faster. I wish silicon could come out quicker. … This is the reality of where we are.”

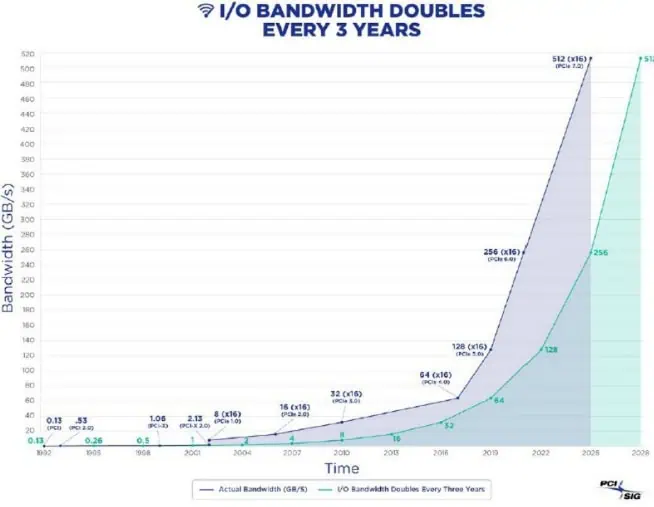

Solomon also mentioned that PCI-SIG has been able to stay ahead of industry demand. As seen in the chart below, the bandwidth capabilities in the PCI-Express 6.0 and 7.0 specifications are about three years ahead of the pace of doubling I/O bandwidth every three years, despite the late release of the 4.0 specification.

“Some of you have been around long enough to point out the small issues with PCI-Express 4.0 and lament over it… but in the past few years, we have managed to maintain a three to four-year gap between establishing this specification and the industry truly needing the bandwidth,” he said. “There are always parts of the ecosystem that need more bandwidth. However, we have done a great job staying at the top of this curve and continuing to develop reliable specifications that people can use.”

Disclaimer: This article is created by the original author. The content of the article represents their personal opinions. Our reposting is for sharing and discussion purposes only and does not imply our endorsement or agreement. If you have any objections, please get in touch with us through the provided channels.